意法半导体(STMicroelectronics,简称ST)宣布针对高性能应用进一步扩大其广受赞誉的SPEAr®(结构化处理器增强型架构)微处理器产品阵容。这一战略举措,旨在为日益复杂且要求严苛的计算机网络工程设计提供更强大、更灵活、更具能效的核心计算引擎。

随着云计算、边缘计算、工业物联网和5G通信的飞速发展,现代网络基础设施正面临前所未有的挑战。网络设备,如高端路由器、多层交换机、网络安全网关、网络附加存储以及无线接入点控制器等,不仅需要处理海量数据的快速转发与交换,还需集成复杂的协议处理、深度包检测、流量管理、虚拟化及安全加密功能。传统的通用处理器或单一架构的芯片往往难以在性能、功耗、集成度和成本之间取得最佳平衡。

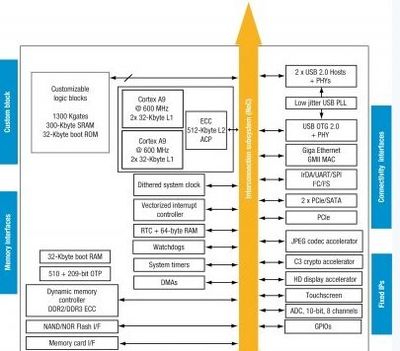

ST此次扩大的SPEAr微处理器系列,正是瞄准了这一市场痛点。SPEAr系列以其高度可配置的异构多核架构著称,通常集成了高性能的ARM应用处理器内核、专用的网络协处理单元以及丰富的高速接口。新的产品阵线预计将在以下方面为计算机网络工程设计带来革新:

- 性能跃升与能效优化:新器件将采用更先进的制程工艺,集成更高主频的多核ARM Cortex-A系列处理器,并强化硬件加速引擎。这使得设备在运行路由协议栈、防火墙规则、VPN加解密等任务时,能够实现极高的吞吐量和极低的延迟,同时保持优异的每瓦特性能比,满足绿色数据中心和边缘节点的节能需求。

- 高度集成与设计简化:新产品将提供更丰富的外设接口集成,如多端口万兆以太网控制器、PCIe Gen3/4接口、USB 3.0、SATA 3.0等。这种高度集成的SoC(片上系统)设计,极大减少了工程师所需的外部元件数量,简化了电路板布局,缩短了产品开发周期,并降低了整体系统成本与功耗。

- 增强的灵活性与可编程性:SPEAr架构的“结构化”特性意味着,工程师可以根据特定的网络应用需求,灵活配置硬件加速模块与软件任务的分工。专用的可编程包处理引擎或硬件加速器能够卸载CPU的繁重负载,让CPU更专注于控制平面和管理任务。这种软硬件协同设计模式,为网络设备制造商提供了巨大的差异化创新空间。

- 强化安全功能:网络安全是网络设计的基石。新的SPEAr处理器预计将内置更强大的硬件安全模块,支持可信执行环境、安全启动、加密算法加速以及防篡改机制,从芯片层面为网络设备构筑坚实的安全起点,符合日益严格的市场法规要求。

对计算机网络工程设计的影响

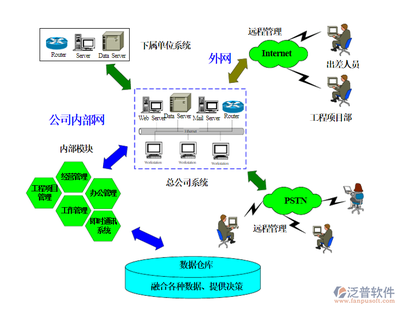

对于网络设备设计工程师而言,ST扩大SPEAr产品线意味着拥有了更多样化的核心平台选择。在设计下一代企业级交换机、运营商级接入设备、智能网卡或网络安全设备时,工程师可以:

- 精准匹配性能需求:从中小型企业到大型数据中心,不同层级的网络设备都能找到性能与成本相匹配的SPEAr解决方案。

- 加速产品上市:借助ST提供的完整参考设计、软件开发套件和成熟的软件生态系统,可以大幅减少底层驱动和基础协议的开发工作,将精力集中于高附加值的功能创新。

- 实现前瞻性设计:芯片强大的处理能力和接口扩展性,使得设计的设备能够平滑适应未来网络协议升级和带宽增长的需求,保护投资。

ST扩大其SPEAr微处理器产品阵线,不仅巩固了其在嵌入式网络处理市场的领先地位,更是为应对未来网络挑战提供了关键的半导体解决方案。通过将高性能计算、高度集成、硬件加速和增强安全性融为一体,新的SPEAr系列有望成为推动下一代高性能、高效率、高安全网络设备设计与创新的核心动力,助力全球计算机网络工程向更智能、更敏捷、更可靠的方向演进。